# HM53462 Series

# 65,536-Word x 4-Bit Multiport CMOS Video RAM (with Logic Operation Mode)

#### **■** DESCRIPTION

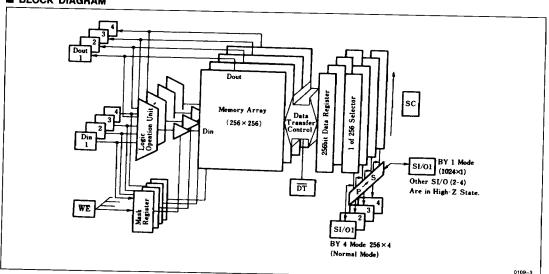

The HM53462 is a 262,144-bit multiport memory equipped with a 64k-word x 4-bit Dynamic RAM port and a 256-word x 4-bit Serial Access Memory (SAM) port. The SAM port is connected to an internal 1,024-bit data register through a 256-word x 4-bit serial read or write access control. In the read transfer cycle, the memory cell data is transferred from a selected word line of the RAM port to the data register. The RAM port has a write mask capability in addition to the conventional operation mode. Write bit selection out of 4 data bit can be achieved. RAM port has another new function, logic operation capability. By this function logic operation between memory data and input data can be done in one cycle. Utilizing the Hitachi 2 µm CMOS process, fast serial access operation and low power dissipation are realized. All inputs and outputs, including clocks, are TTL compatible.

#### **■ FEATURES**

Multiport Organization

(RAM: 64k-word x 4-bit and SAM; 256-word x 4-bit)

- Double Layer Polysilicon/Polyicide N-Well CMOS Process

- Single 5V (±10%)

| Single of (= 10.0)                                        |

|-----------------------------------------------------------|

| Low Power                                                 |

| Active RAM                                                |

| SAM220 mW (max)                                           |

| Standby40 mW (max)                                        |

| Access Time                                               |

| RAM100 ns/120 ns/150 ns                                   |

| SAM40 ns/40 ns/60 ns                                      |

| Cycle Time                                                |

| Random Read or Write Cycle Time (RAM)190 ns/220 ns/260 ns |

| Serial Read or Write Cycle Time (SAM)40 ns/40 ns/60 ns    |

| TTL Compatible                                            |

| • 256 Refresh Cycles                                      |

· Refresh Function RAS Only Refresh CAS Before RAS Refresh Hidden Refresh

- Bidirectional Data Transfer Operation (RAM ←→ SAM)

- Fast Serial Access Operation Asynchronized with RAM Port except Data Transfer Cycle

- · Real Time Read Transfer Capability

- Write Mask Mode Capability

- · Logic Operation Capability between Din and Dout

- SAM Organization Can Be Changed to 1024 x 1

#### **■ ORDERING INFORMATION**

| Part No.     | Access Time | Package        |

|--------------|-------------|----------------|

| HM53462P-10  | 100 ns      | 400 mil 24-pin |

| HM53462P-12  | 120 ns      | Plastic DIP    |

| HM53462P-15  | 150 ns      | (DP-24A)       |

| HM53462ZP-10 | 100 ns      | 24-pin         |

| HM53462ZP-12 | 120 ns      | Plastic DIP    |

| HM53462ZP-15 | 150 ns      | (ZP-24)        |

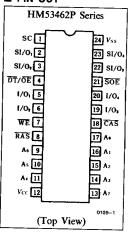

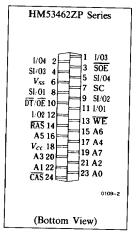

#### PIN OUT

# ■ PIN DESCRIPTION

| Pin Name                             | Function                    |

|--------------------------------------|-----------------------------|

| $A_0 - A_7$                          | Address Input               |

| I/O <sub>1</sub> -I/O <sub>4</sub>   | RAM Port Data Input/Output  |

| SI/O <sub>1</sub> -SI/O <sub>4</sub> | SAM Port Data Input/Output  |

| RAS                                  | Row Address Strobe          |

| CAS                                  | Column Address Strobe       |

| SC                                   | Serial Clock                |

| WE                                   | Write Enable                |

| DT/OE                                | Data Transfer/Output Enable |

| SOE                                  | SAM Port Enable             |

| $v_{CC}$                             | Power Supply                |

| V <sub>SS</sub>                      | Ground                      |

# ■ BLOCK DIAGRAM

#### **■ ABSOLUTE MAXIMUM RATINGS**

| Parameter                                        | Symbol           | Value          | Unit |

|--------------------------------------------------|------------------|----------------|------|

| Voltage on Any Pin Relative to VSS               | v <sub>T</sub>   | - 1.0 to + 7.0 | v    |

| Power Supply Voltage Relative to V <sub>SS</sub> | v <sub>cc</sub>  | -0.5 to $+7.0$ | v    |

| Operating Temperature                            | T <sub>opr</sub> | 0 to + 70      | °C   |

| Storage Temperature                              | T <sub>stg</sub> | - 55 to + 125  | °C   |

| Short Circuit Output Current                     | I <sub>out</sub> | 50             | mA   |

| Power Dissipation                                | P <sub>T</sub>   | 1.0            | w    |

#### ■ INPUT/OUTPUT CAPACITANCE

| Parameter | Symbol          | Тур | Max | Unit | Note |

|-----------|-----------------|-----|-----|------|------|

| Address   | $c_{I1}$        | _   | 5   | pF   |      |

| Clocks    | C <sub>I2</sub> | _   | 5   | pF   |      |

| I/O, SI/O | $c_{I/O}$       | _   | 7   | pF   |      |

### ■ ELECTRICAL CHARACTERISTICS

### • Recommended DC Operating Conditions (T<sub>A</sub> = 0 to +70°C)

| Parameter          | Symbol          | Min   | Тур | Max | Unit | Note |

|--------------------|-----------------|-------|-----|-----|------|------|

| Supply Voltage     | v <sub>cc</sub> | 4.5   | 5.0 | 5.5 | v    |      |

| Input High Voltage | v <sub>IH</sub> | 2.4   | _   | 6.5 | v    |      |

| Input Low Voltage  | v <sub>IL</sub> | - 0.5 | _   | 0.8 | v    | 2    |

Notes: 1. All voltages referenced to  $V_{SS}$ . 2. -3.0V for pulse width  $\leq 10$  ns.

• DC Electrical Characteristics ( $T_A = 0$  to  $+70^{\circ}$ C,  $V_{CC} = 5V \pm 10\%$ ,  $V_{SS} = 0V$ )

| DAM D                                                                | C                 | SAM     | Port   | HM53462 | HM53462 | HM53462 | Unit | Note |

|----------------------------------------------------------------------|-------------------|---------|--------|---------|---------|---------|------|------|

| RAM Port                                                             | Symbol            | Standby | Active | -10     | -12     | -15     | Unit | Note |

| Operating Current RAS, CAS Cycling                                   | I <sub>CC1</sub>  |         | ×      | 70      | 60      | 50      | mA   |      |

| $t_{RC} = min$                                                       | I <sub>CC7</sub>  | ×       | _      | 110     | 100     | 80      | mA   |      |

| Standby Current RAS, CAS = V <sub>IH</sub>                           | I <sub>CC2</sub>  | _       | ×      | 7       | 7       | 7       | mA   |      |

| Standby Current RAS, CAS = VIH                                       | I <sub>CC8</sub>  | ×       | _      | 40      | 40      | 30      | mA   |      |

| RAS Only Refresh Current                                             | I <sub>CC3</sub>  | _       | ×      | 60      | 50      | 40      | mA   |      |

| $\overline{CAS} = V_{IH}$ , $\overline{RAS}$ Cycling $t_{RC} = \min$ | I <sub>CC9</sub>  | ×       | _      | 100     | 90      | 70      | mA   |      |

| Page Mode Current RAS = VII.                                         | I <sub>CC4</sub>  | _       | ×      | 50      | 40      | 35      | mA.  |      |

| $\overline{\text{CAS}}$ Cycling $t_{\text{PC}} = \min$               | I <sub>CC10</sub> | ×       | _      | 90      | 80      | 65      | mA   |      |

| CBR Refresh Current RAS Cycling                                      | I <sub>CC5</sub>  | _       | Х      | 60      | 50      | 40      | mA.  |      |

| $t_{RC} = min$                                                       | I <sub>CC11</sub> | ×       | _      | 100     | 90      | 70      | mA.  |      |

| Data Transfer Current                                                | I <sub>CC6</sub>  | _       | ×      | 75      | 65      | 55      | mA   |      |

| $\overline{RAS}$ , $\overline{CAS}$ Cycling $t_{RC} = \min$          | I <sub>CC12</sub> | ×       |        | 115     | 105     | 85      | mA   |      |

| Parameter                                    | Symbol          | Min  | Max | Unit | Note |

|----------------------------------------------|-----------------|------|-----|------|------|

| Input Leakage                                | I <sub>LI</sub> | - 10 | 10  | μΑ   |      |

| Output Leakage                               | I <sub>LO</sub> | - 10 | 10  | μΑ   |      |

| Output High Voltage I <sub>OH</sub> = - 2 mA | v <sub>OH</sub> | 2.4  |     | v    |      |

| Output Low Voltage I <sub>OL</sub> = 4.2 mA  | V <sub>OL</sub> | T —  | 0.4 | v    |      |

# • Electrical Characteristics and Recommended AC Operating Conditions

$(T_A = 0 \text{ to } +70^{\circ}\text{C}, V_{CC} = 5\text{V} \pm 10\%, V_{SS} = 0\text{V})^{1, 10, 11}$

| Domony                                            | Symbol            | HM53 | 462-10 | HM53 | 462-12 | HM53 | 462-15 | Unit | Note                                             |

|---------------------------------------------------|-------------------|------|--------|------|--------|------|--------|------|--------------------------------------------------|

| Parameter                                         | Symbol            | Min  | Max    | Min  | Max    | Min  | Max    | Cint | Non                                              |

| Random Read or Write Cycle Time                   | t <sub>RC</sub>   | 190  | _      | 220  |        | 260  | _      | ns   |                                                  |

| Read-Modify-Write Cycle Time                      | t <sub>RWC</sub>  | 260  | _      | 300  | _      | 355  |        | пѕ   |                                                  |

| Page Mode Cycle Time                              | tPC               | 70   | _      | 85   | _      | 105  |        | ns   |                                                  |

| Access Time from RAS                              | tRAC              | _    | 100    | _    | 120    |      | 150    | ns   | 2, 3                                             |

| Access Time from CAS                              | t <sub>CAC</sub>  | -    | 50     | _    | 60     | _    | 75     | ns   | 3, 4                                             |

| Outout Buffer Turn-off Delay<br>Referenced to CAS | t <sub>OFF1</sub> | 0    | 25     | 0    | 30     | 0    | 40     | ns   | 5                                                |

| Transition Time (Rise and Fall)                   | t <sub>T</sub>    | 3    | 50     | 3    | 50     | 3    | 50     | ns   | 6                                                |

| RAS Precharge Time                                | trp               | 80   | _      | 90   | _      | 100  | _      | ns   |                                                  |

| RAS Pulse Width                                   | tRAS              | 100  | 10000  | 120  | 10000  | 150  | 10000  | ns   |                                                  |

| CAS Pulse Width                                   | tCAS              | 50   | 10000  | 60   | 10000  | 75   | 10000  | ns   |                                                  |

| RAS to CAS Delay Time                             | tRCD              | 25   | 50     | 25   | 60     | 30   | 75     | ns   | 7                                                |

| RAS Hold Time                                     | t <sub>RSH</sub>  | 50   | _      | 60   | _      | 75   | _      | ns   |                                                  |

| CAS Hold Time                                     | t <sub>CSH</sub>  | 100  | _      | 120  | _      | 150  | _      | ns   |                                                  |

| CAS to RAS Precharge Time                         | tCRP              | 10   | _      | 10   | _      | 10   |        | ns   |                                                  |

| Row Address Setup Time                            | tASR              | 0    |        | 0    | _      | 0    |        | ns   |                                                  |

| Row Address Hold Time                             | tRAH              | 15   |        | 15   | _      | 20   | _      | ns   |                                                  |

| Column Address Setup Time                         | tASC              | 0    |        | 0    |        | 0    | _      | ns   |                                                  |

| Column Address Hold Time                          | t <sub>CAH</sub>  | 20   |        | 20   |        | 25   | _      | ns   | ļ —                                              |

| Write Command Setup Time                          | twcs              | 0    |        | 0    |        | 0    |        | ns   | 1                                                |

| Write Command Hold Time                           | twcs              | 25   |        | 25   |        | 30   |        | ns   | $\vdash$                                         |

| Write Command Pulse Width                         | twp               | 15   |        | 20   |        | 25   |        | ns   | t                                                |

| Write Command to RAS Lead Time                    |                   | 35   |        | 40   |        | 45   |        | ns   | $\vdash$                                         |

| Write Command to CAS Lead Time                    | tRWL              | 35   | -      | 40   |        | 45   |        | ns   | <del>                                     </del> |

| Data-in Setup Time                                | tes               | 0    |        | 0    |        | 0    |        | ns   | ١,                                               |

| Data-in Secup Time  Data-in Hold Time             | t <sub>DS</sub>   | 25   |        | 25   |        | 30   |        | ns   | 8,                                               |

|                                                   | t <sub>DH</sub>   | 0    |        | 0    |        | 0    |        | ns   | <del>  "</del>                                   |

| Read Command Setup Time                           | tRCS              | -    |        | 0    |        | 0    |        | ns   | ┼                                                |

| Read Command Hold Time                            | tRCH              | 0    |        | 0    |        | - 0  |        | 115  | $\vdash$                                         |

| Read Command Hold Time<br>Referenced to RAS       | trrh              | 10   |        | 10   | _      | 10   |        | ns   | _                                                |

| Refresh Period                                    | tREF              |      | 4      |      | 4      |      | 4      | ms   | —                                                |

| RAS Pulse Width<br>(Read-Modify-Write Cycle       | tRWS              | 170  | 10000  | 200  | 10000  | 245  | 10000  | ns   |                                                  |

| CAS to WE Delay                                   | tCWD              | 85   |        | 100  |        | 125  |        | ns   |                                                  |

| CAS Setup Time<br>(CAS Before RAS Refresh)        | t <sub>CSR</sub>  | 10   | _      | 10   |        | 10   | _      | ns   |                                                  |

| CAS Hold Time<br>(CAS Before RAS Refresh)         | tCHR              | 20   | _      | 25   | _      | 30   | _      | ns   |                                                  |

| RAS Precharge to CAS Hold Time                    | trpc              | 10   |        | 10   |        | 10   |        | ns   |                                                  |

| CAS Precharge Time                                | t <sub>CP</sub>   | 10   | _      | 15   |        | 20   |        | ns   |                                                  |

| Access Time from OE                               | toac              | _    | 30     |      | 35     |      | 40     | ns   |                                                  |

| Output Buffer Turn-off Delay<br>Referenced to OE  | t <sub>OFF2</sub> | 0    | 25     | 0    | 30     | 0    | 40     | ns   |                                                  |

| OE to Data-in Delay Time                          | todd              | 25   | _      | 30   | _      | 40   |        | ns   |                                                  |

| OE Hold Time Referenced to WE                     | toeh              | 10   |        | 15   | _      | 20   |        | ns   |                                                  |

987

### • Electrical Characteristics and Recommended AC Operating Conditions (continued)

(T<sub>A</sub> = 0 to +70°C,  $V_{CC}$  = 5V  $\pm$  10%,  $V_{SS}$  = 0V)1, 10, 11

| _                                            |                  | <b>HM</b> 53 | 462-10   | HM53 | 462-12 | HM53 | 462-15       |      |      |

|----------------------------------------------|------------------|--------------|----------|------|--------|------|--------------|------|------|

| Parameter                                    | Symbol           | Min          | Max      | Min  | Max    | Min  | Max          | Unit | Note |

| Data-in to CAS Delay Time                    | t <sub>DZC</sub> | 0            | _        | 0    | _      | 0    | _            | ns   |      |

| Data-in to OE Delay Time                     | t <sub>DZO</sub> | 0            | _        | 0    |        | 0    |              | ns   |      |

| OE to RAS Delay Time                         | tORD             | 35           | _        | 40   | _      | 45   | _            | ns   |      |

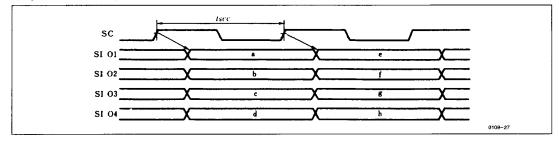

| Serial Clock Cycle Time                      | tSCC             | 40           | _        | 40   | _      | 60   |              | ns   |      |

| Access Time from SC                          | tSCA             | _            | 40       | _    | 40     | _    | 60           | ns   | 10   |

| Access Time from SOE                         | tSEA             | _            | 25       | _    | 30     | _    | 40           | ns   | 10   |

| SC Pulse Width                               | t <sub>SC</sub>  | 10           | _        | 10   | _      | 10   | _            | ns   |      |

| SC Precharge Width                           | tSCP             | 10           | _        | 10   | _      | 10   | -            | ns   |      |

| Serial Data-out Hold Time<br>after SC High   | tson             | 10           |          | 10   | _      | 10   | _            | ns   |      |

| Serial Output Buffer Turn-off Delay from SOE | t <sub>SEZ</sub> | 0            | 25       | 0    | 25     | 0    | 30           | ns   |      |

| Serial Data-in Setup Time                    | tSIS             | 0            |          | 0    |        | 0    |              | ns   |      |

| Serial Data-in Hold Time                     | t <sub>SIH</sub> | 15           | _        | 20   | _      | 25   | <del>-</del> | ns   |      |

| DT to RAS Setup Time                         | t <sub>DTS</sub> | 0            | _        | 0    | _      | 0    |              | ns   |      |

| DT to RAS Hold Time<br>(Read Transfer Cycle) | t <sub>RDH</sub> | 80           | _        | 90   |        | 110  | _            | ns   |      |

| DT to RAS Hold Time                          | t <sub>DTH</sub> | 15           | _        | 15   | _      | 20   | _            | ns   |      |

| DT to CAS Hold Time                          | <sup>‡</sup> CDH | 20           | _        | 30   | _      | 45   | _            | ns   |      |

| Last SC to DT Delay Time                     | t <sub>SDD</sub> | 5            | _        | 5    | _      | 10   |              | ns   |      |

| First SC to DT Hold Time                     | t <sub>SDH</sub> | 25           |          | 25   |        | 30   | _            | ns   |      |

| DT to RAS Delay Time                         | † <sub>DTR</sub> | 10           | _        | 10   | _      | 10   | _            | ns   |      |

| WE to RAS Setup Time                         | tws              | 0            | _        | 0    | _      | 0    | _            | ns   |      |

| WE to RAS Hold Time                          | twH              | 15           |          | 15   | _      | 20   | _            | ns   |      |

| I/O to RAS Setup Time                        | tMS              | 0            | _        | 0    | _      | 0    | _            | ns   |      |

| I/O to RAS Hold Time                         | t <sub>MH</sub>  | 15           | _        | 15   | _      | 20   | -            | ns   |      |

| Serial Output Buffer Turn-off Delay from RAS | tSRZ             | 10           | 50       | 10   | 60     | 10   | 75           | ns   |      |

| SC to RAS Setup Time                         | tSRS             | 30           | _        | 40   |        | 45   |              | ns   |      |

| RAS to SC Delay Time                         | tSRD             | 25           |          | 30   | _      | 35   | _            | пs   |      |

| Serial Data Input Delay Time from RAS        | tSID             | 50           | _        | 60   | _      | 75   | _            | ns   |      |

| Serial Data Input to DT Delay Time           | t <sub>SZD</sub> | 0            |          | 0    | _      | 0    | _            | ns   |      |

| SOE to RAS Setup Time                        | t <sub>ES</sub>  | 0            | <u> </u> | 0    | _      | 0    | _            | ns   |      |

| SOE to RAS Hold Time                         | t <sub>EH</sub>  | 15           | _        | 15   |        | 20   |              | ns   |      |

| Serial Write Enable Setup Time               | tsws             | 0            | _        | 0    | _      | 0    |              | ns   |      |

| Serial Write Enable Hold Time                | tswH             | 35           |          | 35   | _      | 55   | _            | ns   |      |

| Serial Write Disable Setup Time              | tswis            | 0            | _        | 0    |        | 0    | _            | ns   |      |

| Serial Write Disable Hold Time               | tswih            | 35           | _        | 35   |        | 55   |              | ns   |      |

| DT to Sout in Low-Z Delay Time               | tDLZ             | 5            | _        | 10   | _      | 10   | _            | ns   |      |

Notes: 1. AC measurements assume  $t_T = 5$  ns.

- Assumes that t<sub>RCD</sub> ≤ t<sub>RCD</sub> (max). If t<sub>RCD</sub> is greater than the maximum recommended value shown in this table, t<sub>RAC</sub> exceeds the value shown.

- 3. Measured with a load circuit equivalent to 2 TTL loads and 100 pF.

4. Assumes that  $t_{RCD} \ge t_{RCD}$  (max).

- t<sub>OFF</sub> (max) defines the time at which the output achieves the open circuit condition and is not referenced to output voltage levels.

- 6.  $V_{IH}$  (min) and  $V_{IL}$  (max) are reference levels for measuring timing of input signals. Also, transition times are measured between  $V_{IH}$  and  $V_{IL}$ .

- 7. Operation with the t<sub>RCD</sub> (max) limit insures that t<sub>RAC</sub> (max) can be met, t<sub>RCD</sub> (max) is specified as a reference point only, if t<sub>RCD</sub> is greater than the specified t<sub>RCD</sub> (max) limit, then access time is controlled exclusively by t<sub>CAC</sub>.

- 8. t<sub>WC</sub> and t<sub>CWD</sub> are not restrictive operating parameters. They are included in the data sheet as electrical characteristics only: if t<sub>WCS</sub> ≥ t<sub>WCS</sub> (min), the cycle is an early write cycle and the data out pin will remain open circuit (high impedance) throughout the entire cycle; if t<sub>CWD</sub> ≥ t<sub>CWD</sub> (min), the cycle is a read-write and the data output will contain data read from the selected cell; if neither of the above sets of conditions is satisfied, the condition of the data out (at access time) is indeterminate.

- These parameters are referenced to CAS leading edge in early write cycle and to WE leading edge in delayed write or readmodify-write cycles.

- 10. Measured with a load circuit equivalent to 2 TTL and 100 pF.

- 11. After power-up, pause for more than 100 μs and execute at least 8 initialization cycles. Then execute at least one logic reset cycle including write mask reset (on the falling edge of RAS, WE = "Low" and I/O<sub>I</sub>-I/O = "High"), and execute one or more transport cycle for initiation of SAM port.

#### **TIMING WAVEFORMS**

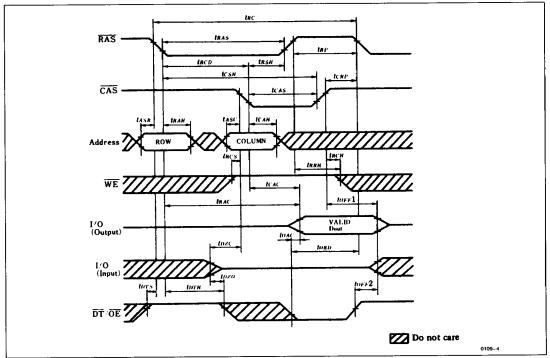

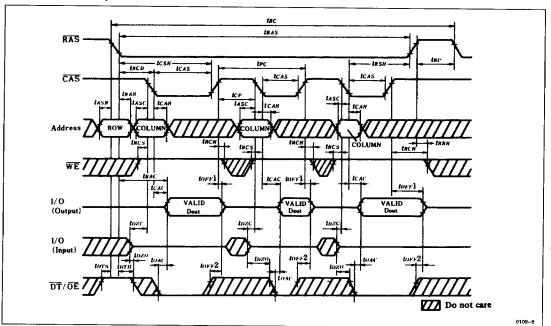

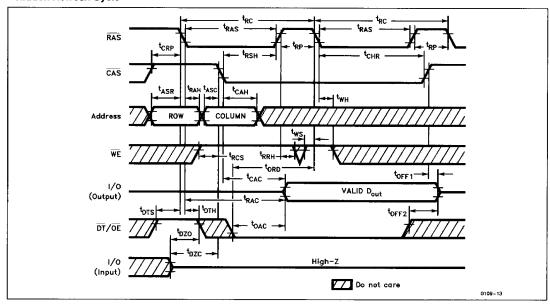

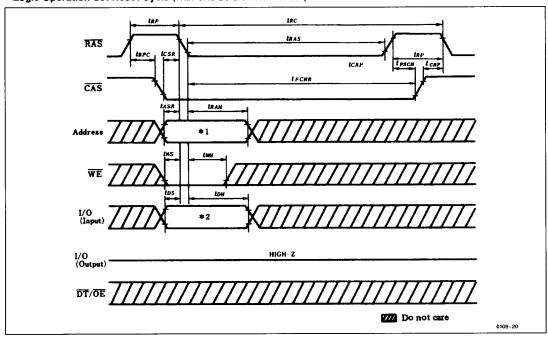

### • Read Cycle

### • Early Write Cycle

Notes: \*1. When WE is "H" level, then all data on the I/O can be written into the cell. When WE is "L" level, the data on the I/O are not written except for when I/O is "H" level at the falling edge of RAS.

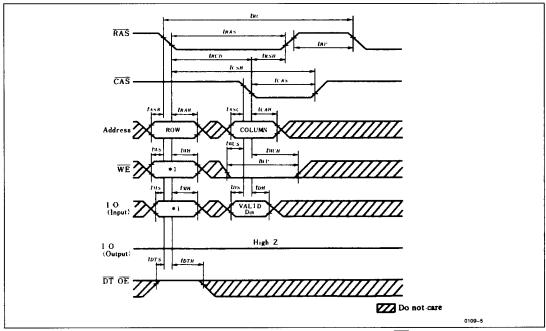

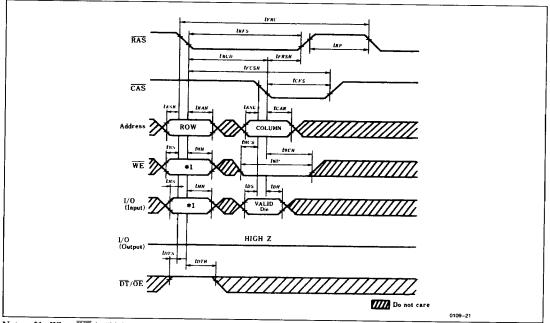

### • Delayed Write Cycle

990

Note: \*1. When WE is "H" level, all the data on I/O<sub>1</sub>-I/O<sub>4</sub> can be written into the memory cell. When WE is "L" level, the data on I/Os are not written except for when I/O = "H" at the falling edge of RAS.

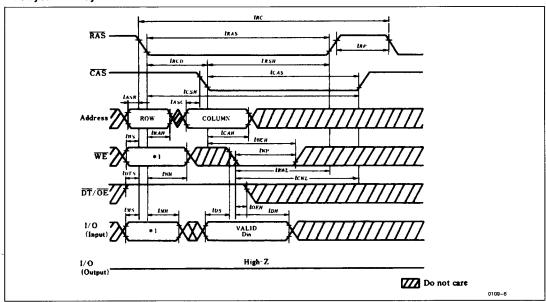

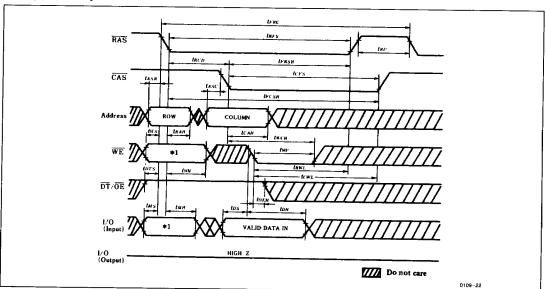

### • Read-Modify-Write Cycle

Note: \*1. When WE is "H" level, all the data on I/O<sub>1</sub>-I/O<sub>4</sub> can be written into the memory cell. When WE is "L" level, the data on I/Os are not written except for when I/O = "H" at the falling edge of RAS.

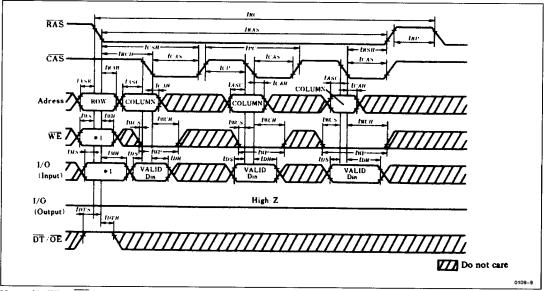

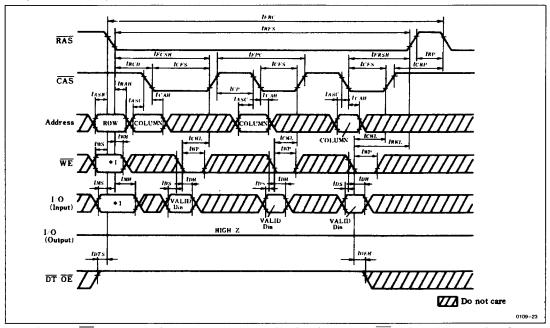

### Page Mode Read Cycle

### • Page Mode Write Cycle (Early Write)

Note: \*1. When WE is "H" level, all the data on I/O<sub>1</sub>-I/O<sub>4</sub> can be written into the memory cell. When WE is "L" level, the data on I/Os are not written except for when I/O = "H" at the falling edge of RAS.

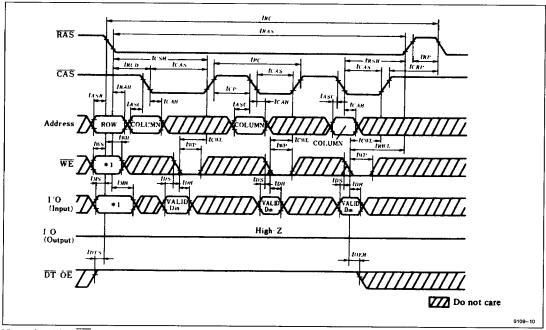

### • Page Mode Write Cycle (Delayed Write)

Note: 1. When WE is "H" level, all the data on I/O<sub>1</sub>-I/O<sub>4</sub> can be written into the memory cell. When WE is "L" level, the data on I/Os are not written except for when I/O = "H" at the falling edge of RAS.

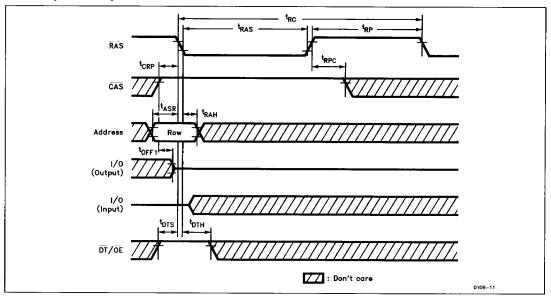

# • RAS Only Refresh Cycle

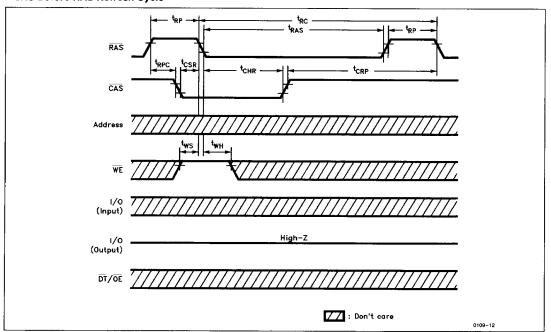

# • CAS Before RAS Refresh Cycle

#### • Hidden Refresh Cycle

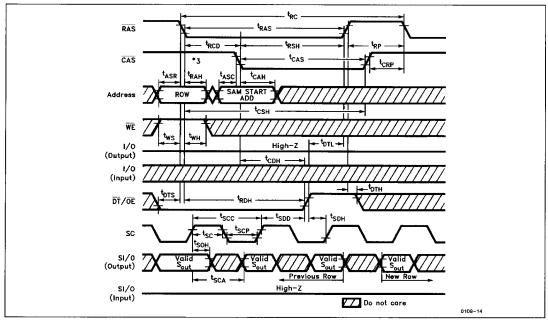

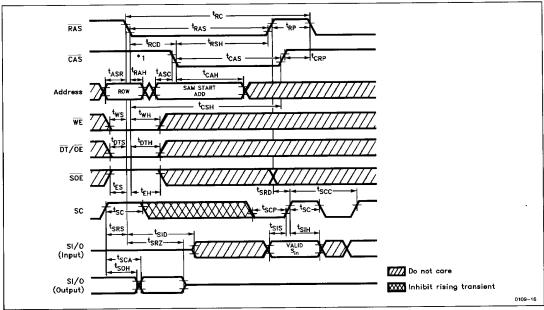

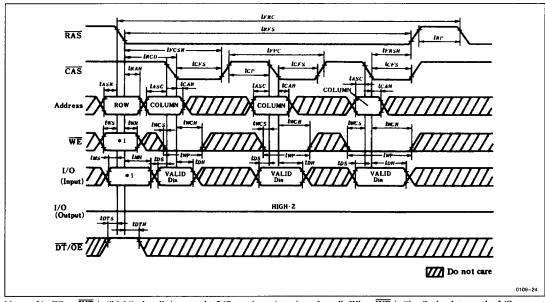

### • Read Transfer Cycle (1)\*1, \*2

Notes: \*1. In the case that the previous data transfer cycle was read transfer.

\*2. Assume that SOE is "Low".

\*3. CAS and SAM start Address need not be supplied every cycle, only when it is desired to change to a new SAM start Address.

# **@HITACHI**

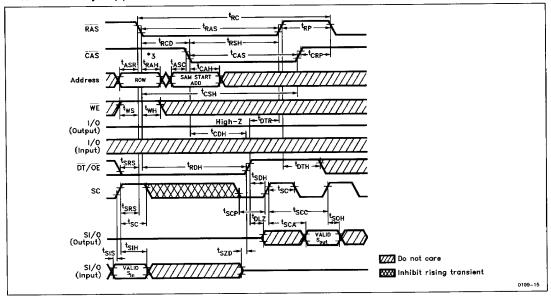

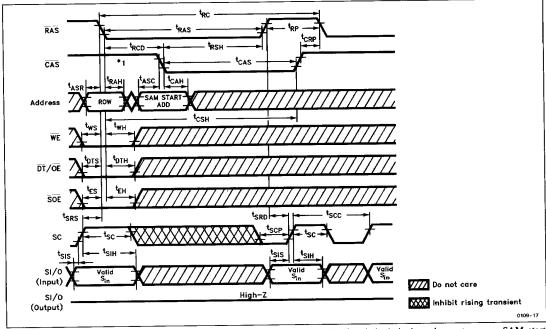

# • Read Transfer Cycle (2)\*1, \*2

Notes: \*1. In the case that the previous data transfer cycle was read transfer.

\*2. Assume that SOE is "Low".

\*3. CAS and SAM start Address need not be supplied every cycle, only when it is desired to change to a new SAM start Address.

### • Pseudo Transfer Cycle

Note: \*1. CAS and SAM start address need not be supplied every cycle, only when it is desired to change to a new SAM start address.

#### • Write Transfer Cycle

Note: \*1. CAS and SAM start address need not be supplied every cycle, only when it is desired to change to a new SAM start address.

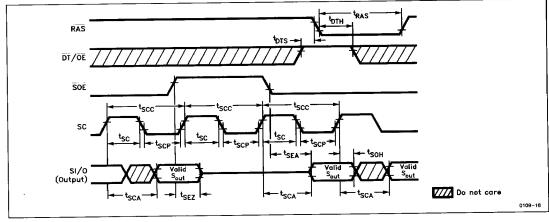

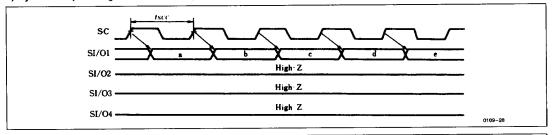

# • Serial Read Cycle

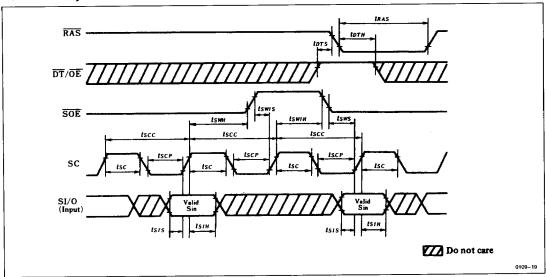

# • Serial Write Cycle

# • Electrical AC Characteristics (Logic Operation Mode)

| _                                                    |                   | HM53 | 462-10 | HM53 | 3462-12 | HM53 | 462-15 | Unit | Note |

|------------------------------------------------------|-------------------|------|--------|------|---------|------|--------|------|------|

| Parameter                                            | Symbol            | Min  | Max    | Min  | Max     | Min  | Max    | Ulli |      |

| Write Cycle Time                                     | tFRC              | 230  | _      | 265  | _       | 310  |        | ns   |      |

| RAS Pulse Width in Write Cycle                       | t <sub>RFS</sub>  | 140  | 10000  | 165  | 10000   | 200  | 10000  | ns   |      |

| CAS Pulse Width in Write Cycle                       | t <sub>CFS</sub>  | 80   | 10000  | 95   | 10000   | 105  | 10000  | ns   |      |

| CAS Hold Time in Write Cycle                         | tFCSH             | 140  |        | 165  | _       | 200  |        | ns   |      |

| RAS Hold Time in Write Cycle                         | tFRSH             | 80   | _      | 95   | _       | 105  |        | ns   |      |

| Page Mode Cycle Time (Write Cycle)                   | tFPC              | 100  | _      | 120  | _       | 135  |        | ns   |      |

| CAS Hold Time<br>(Logic Operation Set/Reset Cycle)   | t <sub>FCHR</sub> | 90   |        | 100  |         | 120  | _      | ns   |      |

| CAS Hold Time from RAS Precharge (x4 → x1 Set Cycle) | t <sub>PSCH</sub> | 10   | _      | 10   | _       | 10   |        | ns   |      |

• Logic Code (FC0-3 are AX0-AX3 in Logic Operation Set Cycle)

|                                       | g p               |   |     | (,  |     |

|---------------------------------------|-------------------|---|-----|-----|-----|

| OGIC                                  | LOGIC             |   |     | FC2 | FC3 |

| Write Data                            | Symbol Write Data |   | FC1 | FC2 | FC3 |

| Zero                                  | 0                 | 0 | 0   | 0   | 0   |

| Di•Mi                                 | ANDI              | 1 | 0   | 0   | 0   |

| Di∙Mi                                 | AND2              | 0 | 1   | 0   | 0   |

| _                                     | X4 → X1           | 1 | 1   | 0   | 0   |

| Di∙Mi                                 | AND3              | 0 | 0   | 1   | 0   |

| Di                                    | THROUGH           | 1 | 0   | 1   | 0   |

| <del>Di</del> •Mi + Di• <del>Mi</del> | EOR               | 0 | 1   | 1   | 0   |

| Di + Mi                               | OR1               | 1 | 1   | 1   | 0   |

| Di∙Mi                                 | NOR               | 0 | 0   | 0   | 1   |

| Di•Mi + Di•Mi                         | ENOR              | 1 | 0   | 0   | 1   |

| Di                                    | INV1              | 0 | 1   | 0   | 1   |

| <del>Di</del> + Mi                    | OR2               | 1 | 1   | 0   | 1   |

| Mi                                    | INV2              | 0 | 0   | 1   | 1   |

| Di + Mi                               | OR3               | 1 | 0   | 1   | 1   |

| <del>Di</del> + <del>Mi</del>         | NAND              | 0 | 1   | 1   | 1   |

| ONE                                   | 1                 | 1 | 1   | 1   | 1   |

- → SAM Organization Changes to 1024 x 1

- → Logic Operation Mode Reset

- Di :External Data-in

- Mi :The Data of the Memory Cell

• Logic Operation Set Reset Cycle (With CAS Before RAS Refresh)

Notes: \*1. Logic code A<sub>0</sub>-A<sub>3</sub> (A<sub>4</sub>-A<sub>7</sub>: don't care)

\*2. Write mask data.

# ■ LOGIC OPERATION MODE

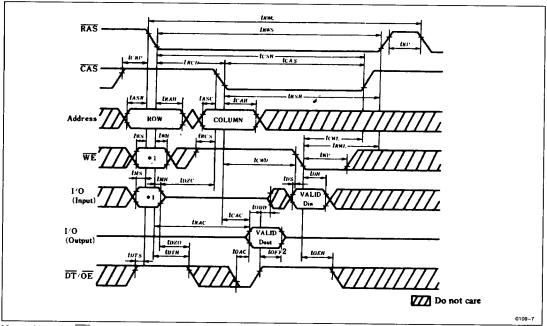

### Early Write Cycle

Note: \*1. When WE is "high", the all data on the I/O can be written into the cell. When WE is "low", the data on the I/O are not written except for when I/O is "high" at the falling edge of RAS.

#### • Delayed Write Cycle

Note: \*1. When WE is "H" level, all the data on I/O<sub>1-4</sub> can be written into the memory cell. When WE is "L" level, the data on I/Os are not written except for when I/O = "H" at the falling edge of RAS.

#### • Page Mode Write Cycle (Delayed Write)

Note: \*1. When WE is "high", the all data on the I/O can be written into the cell. When WE is "low", the data on the I/O are not written except for when I/O is "high" at the falling edge of RAS.

#### • Page Mode Write Cycle (Early Write)

1000

Note: \*1. When  $\overline{WE}$  is "high", the all data on the I/O can be written into the cell. When  $\overline{WE}$  is "low", the data on the I/O are not written except for when I/O is "high" at the falling edge of  $\overline{RAS}$ .

#### ■ DESCRIPTION

#### 1. LOGIC OPERATION MODE

HM53462 has an internal logic operation unit which makes a process of graphics simple. The logic is determined in "Logic operation set/reset cycle", and the operation is executed in every write cycle succeeding to the logic operation set/reset cycle. In this mode the internal read-modify-write operation is executed and the cell data is converted into the new data given by the logic operation between Din and the old cell data.

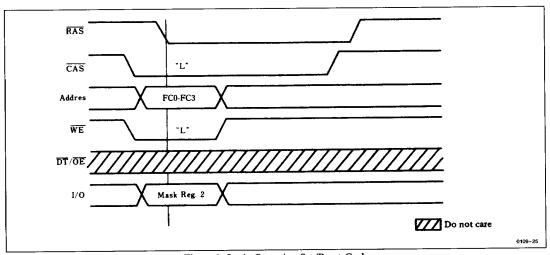

#### 2. LOGIC OPERATION SET/RESET CYCLE

A logic operation set/reset cycle is performed by bringing  $\overline{\text{CAS}}$  and  $\overline{\text{WE}}$  low when  $\overline{\text{RAS}}$  falls (Fig. 1). The logic code and the bits to be masked are determined respectively by AX0-3 state and I/O<sub>1-4</sub> state at the falling edge of  $\overline{\text{RAS}}$ . Furthermore, in this cycle  $\overline{\text{CAS}}$  before  $\overline{\text{RAS}}$  refresh operation is executed, too. In this case of executing the conventional  $\overline{\text{CAS}}$  before  $\overline{\text{RAS}}$  refresh operation,  $\overline{\text{WE}}$  must be high when  $\overline{\text{RAS}}$  falls.

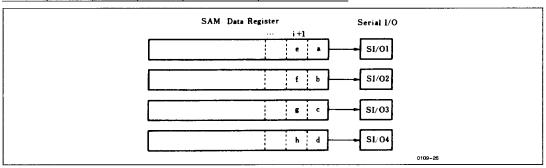

#### 2.1 Logic Code

The logic code is shown in Table 1. When power is turned on, at least one logic reset cycle including write mask reset is required to initialize logic code. If the logic code is (AX3, AX2, AX1, AX0) = (0, 0, 1, 1), the SAM organization is changed converter (Fig. 2). In the case that the SAM organization is changed to 1024 x 1, one data transfer cycle is needed to initialize the SAM selector.

One the SAM organization is changed to 1024 x 1, this code is maintained unless power is turned off.

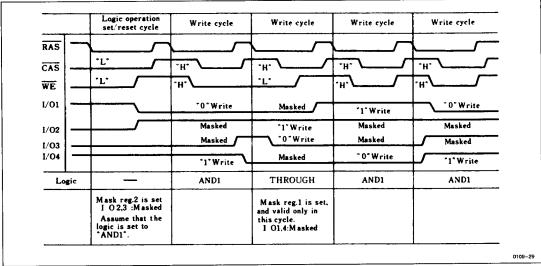

#### 2.2 Write Mask

HM53462 has two kinds of mask registers (register 1, 2). The register 1 is set by bringing WE low at the falling edge of RAS during the write cycle, and the mask data is available only in this cycle. The register 2 is set by level of I/O in the logic operation set/reset cycle, and the mask data is available until the next logic operation set/reset cycle. If the register 1 is set during the current logic operation mode, the mask data of the register 1 is preferred (that of the register 2 is ignored) and the logic becomes "THROUGH" only in this cycle (Fig. 3).

Figure 1. Logic Operation Set/Reset Cycle

### • Table 1. Logic Code (FC0-FC3 are AX0-AX3 in Logic Operation Set Cycle)

| •  | • •                           | -                   |     | •   | •   |     |

|----|-------------------------------|---------------------|-----|-----|-----|-----|

|    | LOGIC                         |                     | ECO | EC. | Eco | FC3 |

|    | Write Data                    | Symbol              | FC0 | FC1 | FC2 | FC3 |

|    | Zero                          | 0                   | 0   | 0   | 0   | 0   |

|    | Di•Mi                         | ANDI                | 1   | 0   | 0   | 0   |

|    | Di∙Mi                         | AND2                | 0   | 1   | 0   | 0   |

| _  |                               | $X4 \rightarrow X1$ | 1   | 1   | 0   | 0   |

|    | Di∙Mi                         | AND3                | 0   | 0   | 1   | 0   |

|    | Di                            | THROUGH             | 1   | 0   | 1   | 0   |

|    | <u>Di</u> •Mi + Di• <u>Mi</u> | EOR                 | 0   | 1   | 1   | 0   |

|    | Di + Mi                       | OR1                 | 1   | 1   | 1   | 0   |

|    | Di∙Mi                         | NOR                 | 0   | 0   | 0   | 1   |

|    | Di•Mi + Di•Mi                 | ENOR                | 1   | 0   | 0   | 1   |

|    | Di                            | INV1                | 0   | 1   | 0   | 1   |

|    | Di + Mi                       | OR2                 | 1   | 1   | 0   | 1   |

|    | Mi                            | INV2                | 0   | 0   | 1   | 1   |

|    | Di + Mi                       | OR3                 | 1   | 0   | 1   | 1   |

| Di | <del>Di</del> + <del>Mi</del> | NAND                | 0   | 1   | 1   | 1   |

| Mi | ONE                           | 1                   | 1   | 1   | 1   | 1   |

- → SAM Organization Changes to 1024 x 1

- → Logic Operation Mode Reset

- Di :External Data-in

- Mi :The Data of the Memory Cell

Figure 2. The Shift Way of SAM Data

#### 1) By 4 Mode (SAM Organization: 256 x 4)

#### 2) By 1 Mode (SAM Organization: 1024 x 1)

Figure 3. Example of Logic Operation Mode