# AN8388S, AN8388SR

# 4 Ch. Linear Driver IC for CD Player

#### Overview

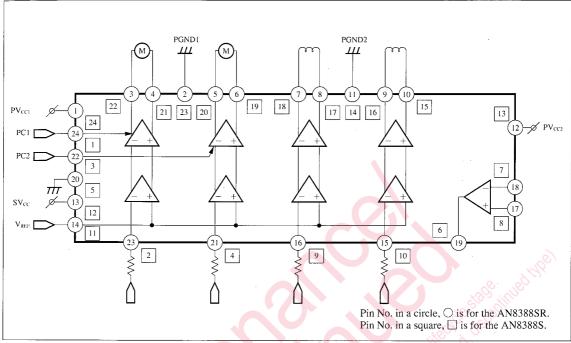

The AN8388S and AN8388SR employ 4 ch. H-bridge system that they are suitable for driving motor or actuator of CD player. Also they employ the surface mounting type package superior in radiation characteristics.

#### Features

- Wide output D-range is available regardless of reference supply on the system.

- 4 ch. BTL Driver built-in. Particularly suitable for driver of actuator or motor of about  $8\,\Omega$  load.

- PC (Power Control) feature built-in

- Thermal shut down circuit (with hysteresis) built-in

- Control for proper heat of IC by separating the power supplies for signal line and output line.

## Application

- CD player, CD-ROM

- For drive of motor

# ■ Absolute Maximum Ratings (Ta=25°C)

| Parameter                     | Symbol           | Rating          | Unit |

|-------------------------------|------------------|-----------------|------|

| Supply Voltage                | SV <sub>cc</sub> | 160             | V    |

| Supply Current                | $I_{CC}$         | 10M; 90         | mA   |

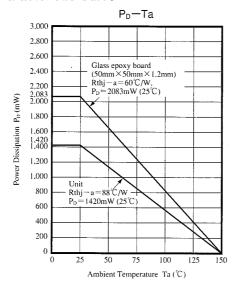

| Power Dissipation Note)       | $P_{D}$          | 2083            | mW   |

| Operating Ambient Temperature | Topr             | -30 ~ +85       | °C   |

| Storage Temperature           | T <sub>stg</sub> | $-55 \sim +150$ | °C   |

Note) For surface mounting on  $50 \times 50 \times 1.2$ mm glass epoxy board

## Recommended Operating Range ( $Ta = 25^{\circ}C$ )

|                                | J \             | ~0′        |

|--------------------------------|-----------------|------------|

| Parameter                      | Symbol          | Range      |

| Operating Supply Voltage Range | V <sub>CC</sub> | 4.5V ~ 15V |

## ■ Electrical Characteristics ( $Ta = 25^{\circ}C \pm 2^{\circ}C$ )

| Parameter                                         | Symbol              | Condition                                                                | min.  | typ.      | max.       | Unit          |  |  |

|---------------------------------------------------|---------------------|--------------------------------------------------------------------------|-------|-----------|------------|---------------|--|--|

| Total Circuit Current                             | $I_{tot}$           | $PV_{CC1} = PV_{CC2} = SV_{CC} = 8V$                                     | 10    | 25        | 40         | mA            |  |  |

| Reset Circuit                                     |                     |                                                                          |       |           |            |               |  |  |

| Reset Operation Release Supply Voltage            | V <sub>RST</sub>    | $R_L = 8 \Omega$                                                         |       |           | 4.5        | V             |  |  |

| Driver 1                                          |                     |                                                                          | ,     |           |            |               |  |  |

| Input Offset Voltage                              | $V_{IOFI}$          | $PV_{CC1} = PV_{CC2} = SV_{CC} = 8V$ $R_L = 8\Omega, R_{IN} = 10k\Omega$ | -10   | _         | 10         | mV            |  |  |

| Output Offset Voltage                             | V <sub>OOF1</sub>   | $PV_{CC1}=PV_{CC2}=SV_{CC}=8V$ $R_{L}=8\Omega, R_{IN}=10k\Omega$         | -60   |           | 60         | mV            |  |  |

| Gain (+)                                          | G <sub>1+</sub>     | $PV_{CC1}=PV_{CC2}=SV_{CC}=8V$ $R_{L}=8\Omega, R_{IN}=10k\Omega$         | 14    | . 17      | 21         | dB            |  |  |

| (+)(-) Relative Gain                              | ⊿Gı                 | $PV_{CC1}=PV_{CC2}=SV_{CC}=8V$ $R_L=8\Omega, R_{IN}=10k\Omega$           | -1.7  | 0         | 1.7        | dB            |  |  |

| Limit Voltage (+)                                 | V <sub>LI+</sub>    | $PV_{CC1} = PV_{CC2} = SV_{CC} = 8V$ $R_L = 8\Omega, R_{IN} = 10k\Omega$ | 4.4   | 4.9       | 5.4        | V             |  |  |

| Limit Voltage (-) Note 1)                         | V <sub>Ll</sub> -   | $PV_{CC1} = PV_{CC2} = SV_{CC} = 8V$ $R_L = 8\Omega, R_{IN} = 10k\Omega$ | 0.93  | 1.0       | 1.07       | -             |  |  |

| Dead Zone Width                                   | $V_{DZI}$           | $PV_{CC1} = PV_{CC2} = SV_{CC} = 8V$ $R_L = 8\Omega, R_{IN} = 10k\Omega$ | -10   | <u>}-</u> | 20         | mV            |  |  |

| PC Operation Threshold H                          | $V_{PCIH}$          | $PV_{CC1} = PV_{CC2} = SV_{CC} = 8V$ $R_L = 8\Omega, R_{IN} = 10k\Omega$ | 3     | 30        | 35 Hilling | V             |  |  |

| Drivers 2 to 4                                    |                     |                                                                          |       |           |            |               |  |  |

| Input Offset Voltage                              | V <sub>IOF</sub>    | $PV_{CC1} = PV_{CC2} = SV_{CC} = 8V$ $R_L = 8\Omega, R_{IN} = 10k\Omega$ | -10   | 100 p     | 10         | mV            |  |  |

| Output Offset Voltage                             | V <sub>OOF</sub>    | $PV_{CC1} = PV_{CC2} = SV_{CC} = 8V$ $R_L = 8\Omega, R_{IN} = 10k\Omega$ | -60   | 94        | 60         | mV            |  |  |

| Gain (+)                                          | G+                  | $PV_{CC1} = PV_{CC2} = SV_{CC} = 8V$ $R_L = 8\Omega, R_{IN} = 10k\Omega$ | 14    | 17        | 21         | dB            |  |  |

| (+)(-)Relative Gain                               | ⊿G                  | $PV_{CC1} = PV_{CC2} = SV_{CC} = 8V$ $R_L = 8\Omega, R_{IN} = 10k\Omega$ | 0.93  | 1.0       | 1.07       |               |  |  |

| Limit Voltage (+) Note 2)                         | $V_{L+}$            | $PV_{CC1} = PV_{CC2} = SV_{CC} = 8V$ $R_L = 8\Omega, R_{IN} = 10k\Omega$ | 0.93  | 1.0       | 1.07       |               |  |  |

| Limit Voltage (-) Note 1)                         | $V_{L-}$            | $PV_{CC1} = PV_{CC2} = SV_{CC} = 8V$ $R_L = 8\Omega, R_{IN} = 10k\Omega$ | 0.93  | 1.0       | 1.07       |               |  |  |

| Dead Zone Width                                   | $V_{DZ}$            | $PV_{CC1} = PV_{CC2} = SV_{CC} = 8V$ $R_L = 8\Omega, R_{IN} = 10k\Omega$ | -10   |           | 20         | mV            |  |  |

| PC Operation Threshold H                          | $V_{PCH}$           | $PV_{CC1} = PV_{CC2} = SV_{CC} = 8V$ $R_L = 8\Omega, R_{IN} = 10k\Omega$ | 3     |           | —          | · V           |  |  |

| Operational amplifier Offset Voltage              | V <sub>OF</sub> -OP | $PV_{CC1} = PV_{CC2} = SV_{CC} = 8V$                                     | -40   |           | 40         | mV            |  |  |

| Heat Protection Circuit                           | Naj Co              | 2).                                                                      |       |           |            |               |  |  |

| Operation Temperature Equilibrium Value Note 3)   | Ттнр                |                                                                          | ( — ) | (160)     | ( — )      | $^{\circ}$    |  |  |

| Operation Temperature Hysteresis<br>Width Note 3) | △T <sub>THD</sub>   |                                                                          | ( )   | ( 65)     | ( — )      | ${\mathbb C}$ |  |  |

Note1) Relative voltage ratio of limit voltage (+) for each channel.

Note2) Relative voltage ratio of limit voltage (+) of Drivers 2 to 4 to limit voltage (+) of Driver 1

Note3) Characteristic value in parentheses is a reference value for design but not a guaranteed value.

#### ■ Characteristic Curve

### Cautions for use

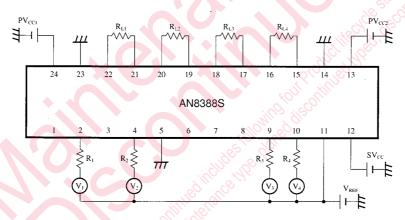

#### AN8388S

When the AN8388S is used, take into account the following cautions and follow the power dissipation characteristic curve.

(1) Load current, IPI flowing in loads RLI and RL2 is supplied through Pin 24.

$$I_{PI} = \frac{|V_{22-21}|}{R_{L1}} + \frac{|V_{20-19}|}{R_{L2}}$$

(2) Load current, IP2 flowing in loads RL3 and RL4 is supplied through Pin 13.

$$I_{P2} = \frac{|V_{18-17}|}{R_{L3}} + \frac{|V_{16-15}|}{R_{L4}}$$

(3) Dissipation increase ( $\Delta P_d$ ) inside the IC (power output stage) caused by loads  $R_{L1}$ ,  $R_{L2}$ ,  $R_{L3}$ , and  $R_{L4}$  is as follows:

$$\begin{split} \varDelta P_{d} &= (PV_{CC1} - |V_{22-21}|) \times \frac{|V_{22-21}|}{R_{Li}} + (PV_{CC1} - |V_{20-19}|) \times \frac{|V_{20-19}|}{R_{L2}} \\ &+ (PV_{CC2} - |V_{18-17}|) \times \frac{|V_{18-17}|}{R_{L3}} + (PV_{CC2} - |V_{16-15}|) \times \frac{|V_{16-15}|}{R_{L4}} \end{split}$$

(4) Dissipation increase (△P<sub>S</sub>) inside the IC (signal block supplied from Pin②) caused by loads R<sub>L1</sub>, R<sub>L2</sub>, R<sub>L3</sub>, and R<sub>L4</sub> is almost as follows:

(5) Dissipation increase inside the IC during driver running is  $\Delta P_d + \Delta P_s$ .

## Cautions for use

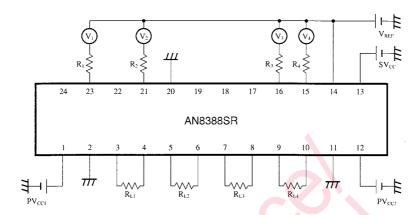

#### AN8388SR

When the AN8388SR is used, take into account the following cautions and follow the power dissipation characteristic curve.

(1) Load current, IPI flowing in loads RLI and RL2 is supplied through Pin 1.

$$I_{PI} = \frac{|V_{3-4}|}{R_{LI}} + \frac{|V_{5-6}|}{R_{L2}}$$

(2) Load current, I<sub>P2</sub> flowing in loads R<sub>L3</sub> and R<sub>L4</sub> is supplied through Pin 2.

$$I_{P2} = \frac{\mid V_{7-8} \mid}{R_{L3}} + \frac{\mid V_{9-10} \mid}{R_{L4}}$$

(3) Dissipation increase (△P<sub>d</sub>) inside the IC (power output stage) caused by loads R<sub>L1</sub>, R<sub>L2</sub>, R<sub>L3</sub> and R<sub>L4</sub> is as follows:

$$\begin{split} \varDelta P_d &= (PV_{CC1} - |V_{3-4}|) \times \frac{|V_{3-4}|}{R_{L1}} + (PV_{CC1} - |V_{5-6}|) \times \quad \frac{|V_{5-6}|}{R_{L2}} \\ &+ (PV_{CC2} - |V_{7-8}|) \times \frac{|V_{7-8}|}{R_{L3}} + (PV_{CC2} - |V_{9-10}|) \times \quad \frac{|V_{9-10}|}{R_{L4}} \end{split}$$

(4) Dissipation increase (△P<sub>S</sub>) inside the IC (signal block supplied from Pin<sup>(3)</sup>) caused by loads R<sub>L1</sub>, R<sub>L2</sub>, R<sub>L3</sub> and R<sub>L4</sub> is almost as follows:

(5) Dissipation increase inside the IC during driver running is,  $\Delta P_d + \Delta P_s$ .

## ■ Pin Description

| Pin No. |          | DC voltage       |     | D: D                       |                                                                                   |                                          |  |

|---------|----------|------------------|-----|----------------------------|-----------------------------------------------------------------------------------|------------------------------------------|--|

| AN8388S | AN8388SR | Symbol           | I/O | (V <sub>CC</sub> /8V)      | Pin Description                                                                   | Equivalent Circuit                       |  |

| 1       | 24       | PC1              | I   | 0V                         | PC (power cut) input pin controlling the output of ② and ②                        | ①                                        |  |

| 3       | 22       | PC2              | I   | 0V                         | PC (power cut) input pin controlling the output of (9) and (20)                   | ***************************************  |  |

| 2       | 23       | IN1              | I   | 2.5V                       | Error input pin of Driver 1                                                       | Ø Ø                                      |  |

| 4       | 21       | IN2              | I   | 2.5V                       | Error input pin of Driver 2                                                       | 2<br>or<br>4<br>or<br>9                  |  |

| 9       | 16       | IN3              | I   | 2.5V                       | Error input pin of Driver 3                                                       | or \$500                                 |  |

| 10      | 15       | IN4              | I   | 2.5V                       | Error input pin of Driver 4                                                       | 10 #                                     |  |

| 7       | 18       | IN-              |     | _ v                        | Reverse rotation input pin of operational amplifier                               | sv <sub>cc</sub>                         |  |

| 8       | 17       | IN+              | I   | Maintenance<br>Maintenance | Normal rotation input pin of operational amplifier                                | 8                                        |  |

| 12      | 13       | SV <sub>CC</sub> | I   | 8V                         | $SV_{CC}$ pin for control circuit of driver, not connected to power $V_{CC}$ pin. | (12)———————————————————————————————————— |  |

| 5       | 20       | SGND             | I   | 0V                         | SGND pin for control circuit of driver                                            | 5 777                                    |  |

Note) The pin numbers shown in the equivalent circuit diagram are only for the AN8388S. For the AN8388SR, they must be replaced.

# Pin Description (Cont.)

| Pin     |          | Symbol            | I/O  | DC voltage            | Pin Description                                                                                                                                 | Equivalent Circuit               |

|---------|----------|-------------------|------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| AN8388S | AN8388SR | J                 |      | (V <sub>CC</sub> /8V) |                                                                                                                                                 |                                  |

| 6       | 19       | ОРО               | 0    | — v                   | Operational amplifier output pin                                                                                                                |                                  |

| 11      | 14       | $V_{ m REF}$      | I    | 2.5V                  | V <sub>REF</sub> input pin                                                                                                                      |                                  |

| 22      | 3        | DI-               | 0    | 0V                    | Reverse rotation output<br>pin of Driver 1                                                                                                      | (PV <sub>(C)</sub> )             |

| 21      | 4        | D1+               | 0    | 0V                    | Normal rotation output<br>pin of Driver 1                                                                                                       | <b>T</b>                         |

| 20      | 5        | D2-               | 0    | 0V                    | Reverse rotation output pin of Driver 2                                                                                                         |                                  |

| 19      | 6        | D2+               | 0    | 0V                    | Normal rotation output<br>pin of Driver 2                                                                                                       | discontinuity of the second      |

| 18      | 7        | D3-               | 0    | 0V                    | Reverse rotation output<br>pin of Driver 3                                                                                                      |                                  |

| 17      | 8        | D3+               | 0    | 0V                    | Normal rotation output pin of Driver 3                                                                                                          |                                  |

| 16      | 9        | D4-               | 0    | 0V                    | Reverse rotation output<br>pin of Driver 4                                                                                                      | 20 16 T 19 15 or or              |

| 15      | 10       | D4+               | 0    | 0V                    | Normal rotation output<br>pin of Driver 4                                                                                                       | ②® <sup>#</sup> <sup>#</sup> ② Ū |

| 24      | 1        | PV <sub>cc1</sub> | I    | 8V                    | Power $V_{cc}$ pin, supplying the current flowing for output power transistors of $\textcircled{1}$ , $\textcircled{2}$ , and $\textcircled{2}$ | (13) or (24)                     |

| 13      | 12       | PV <sub>CC2</sub> | Dist | 8V                    | Power $V_{CC}$ pin, supplying the current flowing for output power transistors of $(3)$ , $(6)$ , $(7)$ , and $(8)$                             |                                  |

| 23      | 2        | PGND1             | ·I   | 0V                    | PGND pin for output transistors of (9, 20, 2), and 22                                                                                           | 14 m                             |

| 14      | 11       | PGND2             | I    | 0V                    | PGND pin for output transistors of (15), (16), (17), and (18)                                                                                   | 23                               |

Note) The pin numbers shown in the equivalent circuit diagram are only for the AN8388S. For the AN8388SR, they must be replaced.

# Request for your special attention and precautions in using the technical information and semiconductors described in this book

- (1) If any of the products or technical information described in this book is to be exported or provided to non-residents, the laws and regulations of the exporting country, especially, those with regard to security export control, must be observed.

- (2) The technical information described in this book is intended only to show the main characteristics and application circuit examples of the products. No license is granted in and to any intellectual property right or other right owned by Panasonic Corporation or any other company. Therefore, no responsibility is assumed by our company as to the infringement upon any such right owned by any other company which may arise as a result of the use of technical information described in this book.

- (3) The products described in this book are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

- Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

- · Any applications other than the standard applications intended.

- (4) The products and product specifications described in this book are subject to change without notice for modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (5) When designing your equipment, comply with the range of absolute maximum rating and the guaranteed operating conditions (operating power supply voltage and operating environment etc.). Especially, please be careful not to exceed the range of absolute maximum rating on the transient state, such as power-on, power-off and mode-switching. Otherwise, we will not be liable for any defect which may arise later in your equipment.

- Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the products.

- (6) Comply with the instructions for use in order to prevent breakdown and characteristics change due to external factors (ESD, EOS, thermal stress and mechanical stress) at the time of handling, mounting or at customer's process. When using products for which damp-proof packing is required, satisfy the conditions, such as shelf life and the elapsed time since first opening the packages.

- (7) This book may be not reprinted or reproduced whether wholly or partially, without the prior written permission of our company.

20080805